## 2.14-GHz 대역 고효율 Class-F 전력 증폭기 개발

# Development of a 2.14-GHz High Efficiency Class-F Power Amplifier

김정준 · 문정환 · 김장헌 · 김일두 · 전명수 · 김범만

Jungjoon Kim · Junghwan Moon · Jangheon Kim · Ildu Kim · Myoungsu Jun · Bumman Kim

#### 요 약

본 논문에서는 Freescale사의 Si-LDMOSFET 4-W 소자를 이용하여 고효율 class-F 전력 증폭기를 구현하였다. Class-F 전력 증폭기를 구현하는데 있어서 모든 하모닉 성분들에 대해 원하는 임피던스를 갖도록 조정하기는 불가능하기 때문에 2차와 3차 하모닉 성분만을 조율하여 회로의 간결함과 동시에 상대적으로 높은 효율을 얻을 수 있었다. 또한, 본 논문에 설계된 증폭기는 보다 정확하게 하모닉 성분을 조율하기 위해, LDMOSFET의 대신호 등가 모델에서 가장 큰 영향을 미치는 drain-source capacitance(Cds)와 bonding inductance(Lb)를 추출하여 하모닉 조율 회로를 설계하였다. 제작된 고효율 class-F 전력 증폭기의 측정 결과 drain-efficiency(DE) 65.1 %, power-added-efficiency(PAE) 60.3 %의 효율을 얻을 수 있었다.

#### **Abstract**

We have implemented a highly efficient 2.14-GHz class-F amplifier using Freescale 4-W peak envelope power(PEP) RF Si lateral diffusion metal-oxide-semiconductor field effect transistor(LDMOSFET). Because the control of the all harmonic contents is very difficult, we have managed only the 2<sup>nd</sup> and 3<sup>rd</sup> harmonics to obtain the high efficiency with simple harmonic control circuit. In order to design the harmonic control circuit accurately, we extracted the bonding wire inductance and drain-source capacitance which are dominant parasitic and package effect components of the device. And then, we have fabricated the class-F amplifier. The measured drain and power-added efficiency are 65.1 % and 60.3 %, respectively.

Key words: Class-F Power Amplifier, LDMOS, High Efficiency, Harmonic Control, Package Effect

## I. 서 론

전력 증폭기는 송신기 단에 가장 핵심적인 부분으로서 전체 효율에 가장 큰 영향을 미치는 요소이다. 전력 증폭기의 효율이 증가하게 되면 기지국 및 중계기 측면에서 냉각 시스템의 사용으로 인한 추가비용을 감소시킬 수 있고, 또한 단말기 측면에서는 배터리의 수명을 증가시킬 수 있다. 그러므로 전력증폭기의 효율은 설계시 고려해야 할 중요한 요소

중 하나라고 할 수 있다.

오랫동안 전력 증폭기의 효율 증대를 위한 연구가 활발하게 진행되어온 가운데 고주파에서도 높은 효율을 성취할 수 있는 대표적인 증폭기로 class-E와 class-F 전력 증폭기에 대한 많은 연구가 있었다. Class-E의 경우, 회로는 비교적 간단한 반면 소자의 전력 밀도가 낮기 때문에 최대 출력 전력이 class-AB의 경우보다 1 dB 정도 낮은 단점이 있다. 반면 Class-F 전력 증폭기의 경우에는 전력 밀도가 높고 외부

<sup>「</sup>This work was supported in part by the Korean Ministry of Education under BK21 project and the center for Broadband OFDM Mobile Access(BrOMA) at POSTECH through the ITRC program of the Korean MIC, supervised by IITA(IITA-2006-C1090-0603-0037).」 포항공과대학교 전자전기공학과(Department of Electronic and Electrical Engineering, Pohang University of Science and Technology (POSTECH))

<sup>·</sup> 논 문 번 호 : 20070518-05S · 수정완료일자 : 2007년 7월 30일

회로만으로 하모닉을 조율하여 효율을 높이기 때문에 쉽게 접근할 수 있으나, 모든 하모닉을 조율할 수 있는 회로를 만든다는 것은 실현 불가능하다는 단점이 존재하다<sup>[1],[2]</sup>.

이론적으로 class-F 전력 증폭기는 모든 하모닉을 조율하여 100 %의 효율을 얻을 수 있지만, 본 논문에서는 효율 향상에 있어서 가장 큰 기여도를 갖는 2차와 3차 하모닉 성분만을 조율하여 회로를 단순화시키면서 동시에 높은 효율을 얻도록 설계되었다. 또한, 보다 정확한 하모닉 조율 회로를 구성하기 위하여 소자 내부의 기생 성분 중에서 가장 영향이 큰 Cds와 Lb 값을 추출하여 하모닉 조율 회로를 설계하였다. 이를 바탕으로 제작된 2.14-GHz 대역의 class-F 전력 증폭기는 측정 결과 drain efficiency(DE) 65.1 %, power-added-efficiency(PAE) 60.3 %의 고효율을 얻을 수 있었다. 이는 지금까지 보고된 LDMO-SFET를 이용한 class-F 전력 증폭기보다 크게 향상된 결과라고 할 수 있다.

#### Ⅱ. Class-F 전력 증폭기

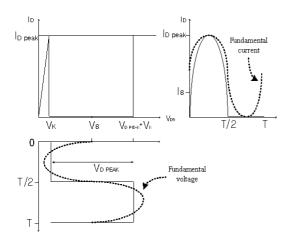

Class-F 전력 증폭기는 class-A나 class-AB와 같은 선형 증폭기 달리, 전압과 전류의 하모닉 성분을 이 용하여 전력 증폭기의 효율을 증가시킨다. 그림 1은 class-F 전력 증폭기의 load-line과 전압 전류의 파형

그림 1. Class-F 전력 증폭기의 load-line 및 전류, 전 압 파형

Fig. 1. The load-line, voltage and current waveforms of class-F PA.

을 나타낸다.

그림 1을 통해 알 수 있듯이, 전압의 홀수 하모닉임피던스를 조율함으로써 사각파 전압 파형을 출력되도록 한다. 이로서 기본 전압 성분을 선형 증폭기에 비해 더 크게 만들 수가 있어 더 큰 전력을 얻을수가 있으며, 동시에 전압과 전류가 겹치게 되는 부분을 최소화 시키게 된다. 소자에서 소모되는 순간DC 전력은 0이 되어, 이상적인 경우 소자에 DC로공급된 전력이 모두 RF 전력으로 변환되어 100 %의효율을 얻게 된다<sup>[3]</sup>.

그림 1의 전류와 전압의 파형을 fourier series로 분석하면 식 (1)과 (2)로 나타낼 수 있다.

$$I_{ds} = i_{d_{peak}} \left( \frac{1}{\pi} + \frac{1}{2} \sin w_0 t - \frac{2}{\pi} \sum_{n=2,4,6,\dots}^{\infty} \frac{1}{n^2 - 1} \cos n w_0 t \right)$$

(1)

$$V_{ds} = V_K + v_{d_peak} \left(\frac{1}{2} - \frac{2}{\pi} \sin w_0 t - \frac{2}{\pi} \sum_{n=3,5,7...}^{\infty} \frac{1}{n} \sin n w_0 t\right)$$

(2)

이상적으로 class-F 전력 증폭기 동작을 위한 전류의 파형은 사인 반파의 모양을 갖게 되고, 이를 fourier series를 통해 전개해 보면 직류 성분, 기본 성분, 그리고 짝수 하모닉으로만 구성된다. 전압의 파형은 사각파 모양을 갖게 되고, 이를 fourier series를 통해 전개해 보면 직류 성분, 기본 성분, 그리고 홀수 하모닉으로만 이루어지게 된다.

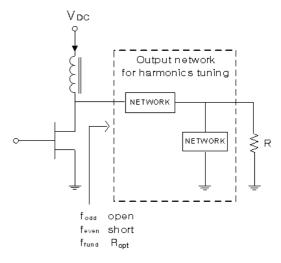

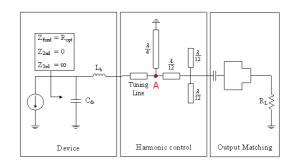

그림 2는 이상적인 class-F 전력 증폭기의 개념적

그림 2. Class-F 전력 증폭기의 이상적인 회로도 Fig. 2. The circuit schematic of ideal class-F PA.

표 1. 하모닉의 증가에 따른 효율 증가 Table 1. Efficiency increase at higher order harmonics.

| I V | 1                 | 3      | 5      | ∞                |

|-----|-------------------|--------|--------|------------------|

| 1   | 50 %<br>Class-A   | 56.3 % | 58.6 % | 63.7 %           |

| 2   | 66.7 %            | 75.0 % | 78.1 % | 84.9 %           |

| 4   | 71.1 %            | 80.0 % | 83.3 % | 90.5 %           |

| ∞   | 78.5 %<br>Class-B | 88.4 % | 92.0 % | 100 %<br>Class-F |

인 회로도이다. 위에서 분석한 사각파의 전압과 사인 반파의 전류 파형을 갖기 위해서는 소자의 drain 단, 즉 종속 전류원 앞에서 홀수 하모닉, 짝수 하모닉의 임피던스를 각각 open과 short 임피던스를 갖도록 만들어 주어 사각파의 전압과 사인 반파의 전류가 생성되도록 한다. 이로서 이상적으로 동작을 할때 소자의 drain단에서는 기본 성분, 홀수 성분 하모닉의 전압 성분만 그리고 짝수 성분 하모닉의 전류성분만이 나타나게 된다<sup>[4]</sup>.

실제적으로 파장에 따라 마이크로 스트립라인의 길이 모두 다르게 보이며 여러 가지 기생 성분들 역시 주파수에 따라 모두 다르게 동작하므로 이상적인 class-F 동작을 위해 모든 하모닉 성분들을 동시에 조율한다는 것은 불가능하다. 하지만 표 1에서 보여지듯이 하모닉 조율 회로가 고차 하모닉 성분들로 확장될수록 효율 향상 정도는 크지 않기 때문에 낮은 차수의 성분만을 조율하더라도 상당히 높은 효율을 얻을 수가 있다<sup>[5]</sup>. 본 논문에서는 class-F 동작을위해 하모닉 성분 중 가장 효율 증가에 가장 큰 영향을 미치는 2, 3차 하모닉만을 조율하여 class-F 전력증폭기를 설계하였다. 2, 3차 하모닉만을 제어한 class-F의 경우, 이론상 약 88 %의 효율 갖게 되지만, 4차 이상의 고차 하모닉 제어 회로 설계의 어려움을고려한다면, 충분히 높은 효율이라고 볼 수 있다<sup>[6]</sup>.

### Ⅲ. Class-F Simulation 및 설계

설계에 사용된 simulator는 Agilent사의 ADS이며 설계와 실험에 사용한 소자는 Freescale사의 4-W 급 Si LDMOSFET MRF281SR1을 사용하였다. MRF- 281SR1의 simulation 모델을 통해 전압, 전류 곡선을 그려본 결과, 소자의 knee 전압이 약 3 V임을 확인할 수 있다. 소자의 출력 전력이 4-W임을 고려할 때 class-B 바이어스 조건에서 소자가 최대 전력을 낼수 있도록 하기 위한 부하 임피던스( $R_{opt}$ )는 식 (3)과 같이 구해진다.

$$R_{opt} = \frac{V_{fund}}{I_{fund}} = \frac{26 \ V - 3 \ V}{0.348 \ A} = 66.09 \ \Omega$$

(3)

여기에서  $V_{fund}$ 와  $I_{fund}$ 는 출력 기본 성분 전압 및 전류의 크기를 나타낸다. Class-F 전력 증폭기의 경우에는 class-B 증폭기와 비교할 때, 전류의 기본 성분은 동일하지만 전압의 기본 성분이  $4/\pi$  배 증가하게 되므로 class-F의  $R_{opt}$ , class-F는  $R_{opt}$ , class-B의  $4/\pi$  배인 84.15  $\Omega$ 이 된다. 하지만 본 논문에서는 홀수 하모닉의 경우 3차 성분까지 조율하기 때문에 1.125배가 증가된 74.35  $\Omega$ 의 임피던스를 가져야만 최대 출력을 얻을 수 있게 된다 $^{[5]}$ .

일반적인 전력 증폭기에서 최대 전력을 내기 위해서는 소자의 종속 전류원에서 바라보는 기본 성분의 임피던스는  $R_{opt}$ 가 되어야 한다. 하지만 소자 내부로 들어가서 볼 수가 없기 때문에 정확한 임피던스확인이 불가능하다. 반면 package 바깥쪽인 electrode에서 하모닉 임피던스를 확인할 수가 있는데, 이는 전력 증폭기 내부의 여러 가지 기생 성분과 함께 package effect가 고려되어 나온 임피던스이다.

본 논문은 소자의 전류원에서 임피던스 확인이불가능하다는 실제적인 상황을 고려하여 electrode에서 소자 내부까지의 기생 성분들을 아래와 같은 방법으로 추출하여 더욱 정확한 설계가 되도록 제안하였다. 동일한 소자인 freescale사의 MRF281SR1으로 PA를 제작하여 실험한 결과를 살펴보면 다음과같은 방법으로 소자 내부를 추측할 수 있다.

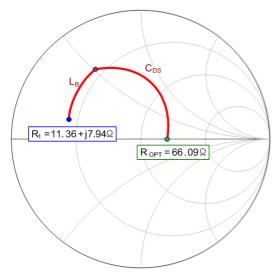

일반적으로 전력 증폭기가 최대 전력을 낼 때 전류원에서 바라보는 임피던스를  $R_{opt}$ 라고 하면, 식 (3)에서와 같이 바이어스 동작 점을 통해 쉽게 계산해낼 수 있다. 또한, 참고 문헌을 통해 실험상 최대 전력을 낼 때 electrode에서 바라본 임피던스는  $Z_L$ = 11.36 + j7.94  $\Omega$ 이라는 값을 얻을 수 있다. 소자 내부에 존재하는 여러 가지 기생 성분들과 함께 package effect의 영향으로 이러한 임피던스 차이가 생기게

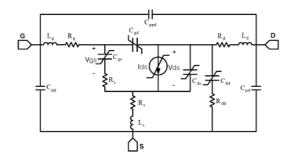

그림 3. LDMOSFET 대신호 등가 회로

Fig. 3. Large signal equivalent circuit of LDMOSFET.

그림 4. 간단한 matching을 통한  $C_{ds}$ 와  $L_b$ 의 추출 Fig. 4. Extract  $C_{ds}$  and  $L_b$  by smith chart matching.

되는데, 이는 대신호 등가 모델을 통해 더욱 자세히 살펴 볼 수가 있다<sup>[7]</sup>.

그림 3은 Si LDMOSFET의 대 신호 등가 회로이다. 앞에서 기생 성분들과 package effect 등이 존재함을 알 수 있는데, 본 논문은 이러한 여러 가지 성분들 중에 가장 큰 영향을 미칠 것이라고 추측할 수 있는  $C_d$ 와  $L_b$ 를 간단한 매칭을 통해 구함으로서 정확한 설계를 도모하였다 $^{[8]}$ .

Class-B 동작시 소자가 최대 전력을 낼 때, 스미스 차트를 통해  $R_1$ (electrode에서 바라본 임피던스)과  $R_{opt}$  사이에 존재하는 여러 가지 매칭 중, 전력이 작은 소자임을 고려하여 가장 간단하면서도 실현 가능할 만한 값을 예측해 본 결과  $C_{ds}$  2.5 pF,  $L_b$  1.3 nH

그림 5. 출력 단 simulation schematic

Fig. 5. Output stage simulation schematic.

을 얻을 수가 있었다. 위 값은 정확한 값은 아니더라 도 불확실한 소자 내부 회로를 예측할 수 있다는 사실만으로 상당히 큰 의미가 있다고 할 수 있다. 또한, 실제 소자를 분해해서  $L_b$ 를 좀 더 정확하게 측정해본 결과 1.1 nH 정도로 스미스 차트를 통해 추측한 값과 상당히 비슷함을 검증할 수가 있었다.

Advanced design system(ADS)를 이용한 simulation 에서 추출된  $C_{ds}$ 와  $L_{b}$ 를 바탕으로 소자 내부를 예측하고 이를 포함하여 출력 단의 매칭 회로와 하모닉 조율 회로를 설계하였다.

그림 5에서는 simulation을 위한 회로 구성도를 보여 준다. 하모닉 조율 회로를 살펴보면, 2차 하모닉의 경우  $\lambda/4$ 라인을 통해 A 지점에서 short을 만들고, 3차 하모닉의 경우에는 두 개의  $\lambda/12$ 라인을 통해 short, 다시 한 개의  $\lambda/12$ 라인을 통해 A 지점에서 open으로 만들게 된다. 이러한 임피던스 정보는소자 내부로 들어가게 되면서 상당히 많이 달라지게되는데 추출된  $C_{ds}$ 와  $L_{b}$ 를 바탕으로 tuning line을 조율해 가며 전류원 앞에서 각 하모닉에 대해 원하는임피던스가 되도록 하였다<sup>19</sup>.

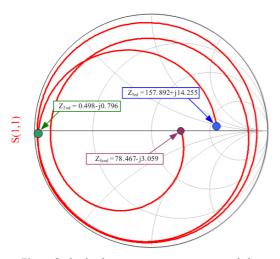

이렇게 구성된 출력단 회로의 S-parameter simulation 결과를 그림 6에서 확인할 수 있다. 그 결과는 2차, 3차 하모닉에서 각각 short에 가까운 작은 임피던스와 상당히 큰 임피던스를 나타내고 있으며, 이를 통해 하모닉 조율 회로가 적절히 설계되었음을 알 수 있다.

기본 성분에 대해서는 소자 내부의 종속 전류원에서  $R_{opt}$ , class-F의 임피던스를 바라보고 출력 단에서최대 전력을 낼 수 있도록 설계하였다. 이렇게 설계

그림 6. 출력 단 회로 S-parameter simulation 결과 Fig. 6. S-parameter simulation results at output stage.

표 2. S-parameter simulation 하모닉 임피던스 Table 2. Harmonic impedance of S-parameter simulation results.

| Harmonic impedance | Fund                      | 2nd                | 3rd                       |

|--------------------|---------------------------|--------------------|---------------------------|

| Ideal              | 74.35 Ω                   | 0 Ω                | 8                         |

| Simulation         | 78.467 $-j3.059 \ \Omega$ | 0.498<br>-j0.796 Ω | 157.892 $-j14.225 \Omega$ |

된 출력단 회로의  $L_b$ ,  $C_{ds}$ 를 제거하고 소자에 연결하 여 simulation한 결과, 출력 전력 37.4 dBm에서 DE와 PAE가 각각 72.6 %, 67.5 % 임을 확인할 수 있었으며 이때 gain은 11.7 dB를 나타내었다.

## Ⅳ. 제작 및 측정

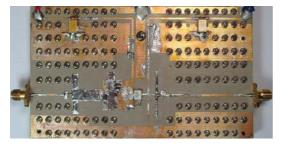

그림 7은 실제 제작된 증폭기를 보인다. Class-F

그림 7. 실제 제작된 Class-F 전력 증폭기 Fig. 7. Realized class-F PA.

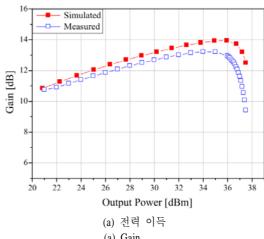

(a) Gain

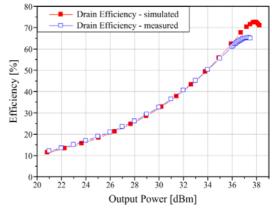

(b) 드레인 효율

(b) Drain efficiency

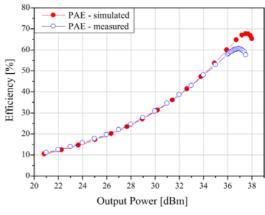

(c) 전력 부가 효율

(c) Power-added efficiency

그림 8. Simulation과 measurement 결과 비교

Fig. 8. Comparison of simulation results and measured results.

증폭기의 bias는  $V_{ds}$ =26 V,  $V_{gs}$ =3.724 V로  $I_q$ 가 0 A인 class-B 전력 증폭기의 bias 조건에서 동작시켰고, 입력은 continuous wave(CW) 신호로 실험을 진행하였다.

그림 8은 simulation 결과 및 측정 결과를 보인다. CW 측정 결과, P<sub>1dB</sub>는 36.79 dBm, 최대 효율은 출력 전력 37.1 dBm에서 DE는 65.1 %, PAE는 60.3 %, gain은 11.3 dB를 확인할 수 있었다. 2 GHz 대역의 고주파로 올라갈수록 LDMOSFET의 성능이 크게 감소하는 것을 감안하면 이는 같은 주파수 대역에서 동일한 소자를 이용한 saturation 전력 증폭기보다 상당히 개선된 결과임을 알 수 있다.

## V. 결 론

본 논문에서는 Freescale사의 4-W PEP Si LDMO-SFET MRF281SR1을 이용하여 2.14-GHz 대역의고효율 class-F 전력 증폭기를 설계 및 제작하였다. Class-F전력 증폭기에서 회로의 간결함을 위해 3차하모닉까지 조율하도록 설계하였다. 또한, 소자 내부의  $C_{ds}$ 와  $L_{b}$ 를 간단한 매칭을 통해 추출하였으며, 이를 고려하여 2차 및 3차 하모닉 조율 회로를 설계하였다.

Simulation 결과, 출력 전력 37.4 dBm에서 DE 72.6 %, PAE 67.5 %의 높은 효율 특성을 얻을 수 있었고, 이때 gain은 11.7 dB였다. 제작된 class-F 전력 증폭기는 출력 전력 37.1 dBm에서 DE 65.1 %, PAE 60.3 %, gain 11.3 dB의 결과를 얻을 수 있었다. 이 결과는 2 GHz 대역 이상에서 LDMOSFET의 성능이 크게 감소하는 것을 감안하면 상당히 개선된 결과임을 알수 있다.

## 참 고 문 헌

[1] A. V. Grebennikov, "Switched-mode tuned highefficiency power amplifiers: historical aspect and

- future prospect", in *IEEE RFIC Symp.*, pp. 49-52, Jun. 2002.

- [2] A. V. Grebennikov, "Circuit design technique for high efficiency class F Amplifier", in *IEEE MTT-S Int. Microw. Symp. Dig.*, vol. 2, pp. 771- 774, Jun. 2000.

- [3] S. C. Cripps, RF Power Amplifiers for Wireless Communications, Norwood, MA: Artech House, 2002.

- [4] Y. Y. Woo, Y. Yang, and B. Kim, "Analysis and experiments for high-efficiency class-F and inverse class-F power amplifiers", *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 5, pp. 1969-1974, May 2006.

- [5] F. H. Raab, "Class-F power amplifiers with maximally flat waveforms", *IEEE Trans. Microw. Theory Tech.*, vol. 45, pp. 2007-2012, Nov. 1997.

- [6] F. H. Raab, "Class-E, class-C, and class-F power amplifiers based upon a finite number of harmonics", *IEEE Trans. Microw. Theory Tech.*, vol. 49, pp. 1462-1468, Aug. 2001.

- [7] Jangheon Kim, Jeonghyeon Cha, Ildu Kim, and Bumman Kim, "Optimum operation of asymmetrical-cells-based linear doherty power amplifiers-uneven power drive and power matching", *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 5, pp. 1802-1809, May 2005.

- [8] Y. Yang, Y. Y. Woo, Jaehyok Yi, and Bumman Kim, "A new empirical large-signal model of Si LDMOSFETs for high-power amplifier design", *IEEE Trans. Microw. Theory Tech.*, vol. 49, no. 9, pp. 1626-1633, Sep. 2001.

- [9] J. Lee, J. Cha, J. Kim, and B. Kim, "Development of a 1 GHz high efficiency class-F power amplifier", 전파 및 광파기술 학술대회, 2004년 10월.

#### 김 정 준

2007년 2월: 한양대학교 전자공학 과 (공학사)

2007년 3월~현재: 포항공과대학교 전자전기공학과 석사과정

[주 관심분야] 고효율 고선형성 RF 전력 증폭기 설계

## 문 정 환

2006년 2월: 서울 시립대학교 전자 공학과 (공학사)

2006년 3월~현재: 포항공과대학교 전자전기공학과 박사과정

[주 관심분야] 고효율 고선형성 RF 전력 증폭기 설계

### 김 장 헌

2003년 2월: 전북대학교 전자공학 과 (공학사)

2003년 3월~현재: 포항공과대학교 전자전기공학과 박사과정

[주 관심분야] 고효율 고선형성 RF 전력 증폭기 설계 및 메모리 영 향 보상 기술 연구, 디지털 전치

왜곡 선형화 기술 연구

#### 김 일 두

송신기 설계

2004년 2월: 전남대학교 전자공학 과 (공학사)

2004년 3월~현재: 포항공과대학교 전자전기공학과 박사과정

[주 관심분야] RF 전력 증폭기 설계 및 선형전력 증폭기(LPA) 시스템 설계, 기지국용 고효율 전력

## 전 명 수

2007년 2월: 부산대학교 전자공학과 (공학사)

2007년 3월~현재: 포항공과대학교 전자전기공학과 석사과정

[주 관심분야] 고효율 광대역 RF 전력 증폭기 설계

#### 김 범 만

1979년 2월: 카네기 멜론대학 전자 공학과 (공학박사)

1978년~1981년: GTE Lab. 연구원 1981년~1988년: TI Central Research Lab. 연구원

1989년~2003년: 포항공과대학교 전 자컴퓨터공학부 정교수

1994년~2004년: 포항공과대학교 마이크로웨이브 응용 연 구센터(MARC, funded by ADD) 센터장

2002년 7월~2005년 6월: T-MTT Associate Editor(IEEE) 2003년 4월~현재: 포항공과대학교 전자컴퓨터공학부 BK 사업 단장

2003년~2004년: 한국과학기술한림원 종신회원 및 공학 부정보통신 분과장

2004년~2005년: 대한전자공학회 협동 부회장

2004년~현재: 포항공과대학교 전자컴퓨터공학부 남고석 좌교수

2005년 1월~2007년 12월: Distinguished Lecturer(IEEE MTT society)

2006년~현재: 포항공과대학교 전자컴퓨터공학부 주임교 수

2007년 1월~현재: IEEE Fellow 선정

[주 관심분야] 이동통신용 전력 증폭기, RF 회로 설계 및 소자 모델링, III-V 화합물 반도체, 초고주파 집적회로 (MMIC) 설계 및 구현, 밀리미터 웨이브 회로 설계